在工业自动化产线、嵌入式控制主板、汽车电子控制单元(ECU)等领域,可编程逻辑器件(Programmable Logic Device,简称PLD)承担着高速信号桥接、定制化数据处理和时序逻辑控制等核心任务-20。无论是工厂流水线上的设备维修人员、嵌入式开发工程师,还是企业质检部门的技术人员,在实际工作中都会遇到一个棘手的问题:如何准确判断一块PLD芯片是好是坏?如果芯片本身是完好的,但存有问题的设计文件(PLD文件)被误编程进去,设备故障将变得扑朔迷离——你甚至无法确定是硬件坏了还是逻辑出错了。掌握PLD文件的查看与验证方法,结合PLD器件的系统性检测流程,可以帮助不同基础的从业者快速定位故障源,避免误判和无效更换,从而大幅提升产线维护和质检效率。本文将从工业嵌入式场景的实际需求出发,分层次详解PLD检测的完整实操流程,兼顾新手入门与专业进阶,助你精准判断PLD器件好坏。

一、PLD文件认知与检测工具准备(适配工业嵌入式场景精准检测)

1. 工业嵌入式PLD检测核心工具介绍

要开展PLD检测,首先要明确:PLD器件本身是一块硬件芯片,而PLD文件则是存储了芯片逻辑配置的编程数据(通常为JEDEC格式的编程文件)。“打开PLD文件”并非像打开Word文档那样双击查看,而是需要使用特定EDA开发软件来加载、查看或验证其逻辑设计内容-3。

基础款工具(新手入门,适配工厂入门质检员/设备维修人员):

万用表:用于PLD芯片供电电压测试、引脚对地导通检测、焊点短路/开路排查,这是最基础也最常用的现场检测工具。工厂新手需重点关注3.3V/5V供电轨电压是否在±5%的工业标准范围内。

示波器:用于观察PLD芯片关键引脚的信号波形、时钟信号质量和电平状态。选择带宽100MHz以上的数字示波器,即可满足大部分工业场景下的PLD信号检测需求。

JTAG下载/调试器:如Altera USB-Blaster、Xilinx Platform Cable等,用于将PLD文件烧录到目标器件,并通过JTAG接口读取器件ID和配置状态。

专业款工具(进阶精准,适配工厂流水线批量检测/专业质检):

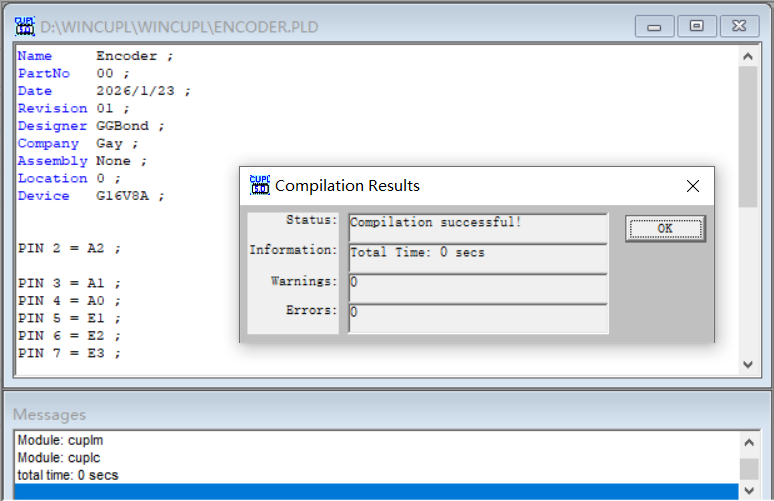

专用EDA开发软件:不同PLD芯片厂商有各自的配套开发工具。例如,TI的PLD配套InterConnect Studio(ICS)提供直观的拖放界面,可进行设计、仿真、配置和器件编程-1;Microchip的WinCUPL II支持SPLD和CPLD的逻辑编译与仿真,可直接生成JEDEC编程文件-3;Altera/Intel Quartus II支持原理图和VHDL设计输入,内置综合器和仿真器-。这类工具不仅是编程工具,更是检测PLD逻辑是否正确的关键平台。

逻辑分析仪:用于捕获和分析PLD的多路数字信号时序关系,检测时序违例和信号完整性问题-。SignalTapII嵌入式逻辑分析仪可直接在FPGA/PLD内部捕获信号波形,无需额外硬件探针,特别适合引脚受限的工业设备-39。

边界扫描控制器:基于JTAG/IEEE 1149.1标准,可对板级PLD进行连通性测试和配置完整性校验,无需物理探针即可检测PLD与PCB焊点的开路/短路-20。

2. 工业嵌入式PLD检测安全注意事项(重中之重)

PLD检测过程中必须严格遵守以下安全规范,避免设备损坏或人身伤害:

断电操作优先:任何涉及PLD拆焊、引脚测量、JTAG连接的操作,必须先切断设备电源,释放残余电荷。工业设备中PLD通常由开关电源供电,断电后电容放电时间约1-2分钟,务必等待电容完全放电后再操作。

静电防护不可省:PLD芯片对静电非常敏感,在干燥的工厂环境中(尤其是秋冬季节),静电放电(ESD)可能导致PLD内部逻辑单元永久损坏-44。操作前必须佩戴静电手环,使用防静电工作台和防静电镊子。

电压测量规范:用万用表测量PLD供电电压时,先将万用表拨到直流电压档(量程20V),黑表笔接地(GND,通常为PCB的铜皮地线或电源负端),红表笔依次触碰VCC引脚。注意不要同时触碰两个相邻引脚造成短路。

JTAG连接确认:连接JTAG下载器前,确认目标设备已断电,下载器与设备之间的排线连接无误。上电后先读取PLD的IDCODE确认连接正常,再执行后续编程操作。错误的JTAG连接可能导致PLD锁死或下载器烧毁。

3. PLD基础认知(适配工业嵌入式精准检测)

在开始检测之前,你需要了解PLD器件的基本结构和关键参数:

PLD的主要类型:简单PLD(SPLD,如GAL)、复杂可编程逻辑器件(CPLD)和现场可编程门阵列(FPGA)。CPLD和FPGA是目前工业嵌入式系统中最常见的两类PLD,前者规模较大、适合复杂逻辑控制,后者集成度更高、适合高速并行处理-。

关键参数与检测的关联:

供电电压(VCC):通常为3.3V、2.5V或1.8V,检测时务必确认供电电压在额定范围内。PLD逻辑功能异常的首要排查方向就是供电问题-44。

I/O电平标准:不同PLD支持LVTTL、LVCMOS、PCI等多种I/O标准,误配会导致信号传输异常。

宏单元/逻辑单元数量:决定了PLD的逻辑容量,超出容量的逻辑设计无法正确烧录。

配置方式:RAM型PLD(如大多数FPGA)每次上电需从外部配置存储器加载数据;Flash型PLD(如CPLD)配置数据保存在芯片内部,掉电不丢失。

PLD文件与器件的关系:PLD文件(如JEDEC、SOF、POF格式)是描述PLD内部逻辑连接的“设计蓝图”。将正确的PLD文件烧录到匹配的PLD芯片中,芯片才能按预期逻辑工作。PLD检测的核心任务包括两方面:一是确认PLD芯片本身的电气性能和物理完好性,二是验证烧录的逻辑是否与预期设计一致。

二、核心检测方法(分层次实操,从入门到进阶)

1. 工业嵌入式PLD基础检测法(现场快速初筛)

无需复杂专业仪器,维修人员在产线现场即可完成的基础检测流程:

第一步:目视检查。 用放大镜或体视显微镜观察PLD芯片的引脚是否有弯曲、断裂、虚焊或连锡现象。特别注意芯片四周引脚与PCB焊盘之间的接触情况,这是最常见的现场故障类型-25。检查芯片表面是否有烧灼痕迹、裂纹或鼓起——这些通常是过压或过流损坏的典型特征-20。

第二步:供电电压检测。 设备通电状态下,用万用表直流电压档测量PLD的VCC引脚与GND之间的电压,确认是否在芯片规格书标称范围内(通常偏差不超过±5%)。工厂产线中,PLD供电异常的原因常常是电源模块电容老化或稳压器损坏。

第三步:对地导通测试。 断电状态下,将万用表拨到蜂鸣档(二极管档),红表笔接地,黑表笔依次触碰PLD的各I/O引脚。若某引脚直接导通(蜂鸣器长鸣),说明该引脚对地短路,通常为内部ESD损坏或外部过压击穿所致。如果多个相邻引脚同时导通,则需排查焊锡连锡问题。

第四步:关键信号波形检查。 用示波器探头夹住GND端,探头尖触碰PLD的时钟输入引脚(CLK)和复位引脚(RST),观察是否有稳定的时钟波形和符合时序要求的复位信号。对于工业控制场景中的PLD,时钟异常是最容易被忽视但影响面最大的故障源。

工业现场判断标准:完成以上四步检测后,若供电正常、无物理短路/开路、时钟和复位信号稳定,但PLD所在电路模块仍不工作,则可初步判定问题可能出在PLD内部的逻辑配置或编程数据上,需要进入下一阶段的专业检测。

2. 万用表/示波器检测PLD方法(新手重点掌握)

结合基础仪器,对PLD进行功能性验证,这是工业维修现场最实用的检测手段。

检测模块一:JTAG通信检测(验证PLD是否可被识别)

将JTAG下载器连接到目标PCB的JTAG接口(通常为5针或10针座,包含TCK、TMS、TDI、TDO、GND五个信号)。

启动配套EDA软件(如Quartus II的Programmer工具),选择对应器件型号。

点击“Auto Detect”或“检测硬件”,观察软件能否成功识别PLD的IDCODE。

判断标准:能读取到正确的IDCODE,说明PLD的JTAG链完整,芯片供电和基本连接正常;无法识别则可能是供电问题、JTAG连接错误或芯片已损坏。

检测模块二:配置完整性验证

在EDA软件中尝试对PLD进行“空白检查”(Blank Check)或“校验”(Verify)。

如果芯片已被编程过,校验结果会显示配置数据是否与参考文件匹配。

判断标准:校验通过说明配置数据完整;校验失败可能是PLD内部配置存储器损坏或编程过程出错。

检测模块三:I/O引脚电平检测(验证逻辑输出是否正确)

查阅PLD的设计文档,获取各I/O引脚在特定输入条件下的预期输出逻辑。

将万用表或示波器探头连接到待测I/O引脚,施加对应的输入激励信号(如通过外部开关或信号发生器产生特定电平)。

观察引脚输出电压,逻辑高电平应接近VCC(不低于VCC×0.7),逻辑低电平应接近GND(不高于0.4V)。

工业场景实用技巧:工厂新手可以通过测量I/O引脚在静态状态下的电平来快速定位异常——某个本应输出高电平的引脚显示为低电平且对地电阻接近0Ω,通常说明该引脚内部ESD单元已击穿。

3. 工业嵌入式专业仪器检测PLD方法(进阶精准检测)

适用于工厂流水线批量检测、专业质检中心和高精度故障定位场景,需要专业的检测仪器和软件环境。

方法一:EDA仿真验证(逻辑功能预检)

在开发环境(如Quartus II、WinCUPL II)中打开PLD的设计源文件(.vhd、.v、.cupl或原理图文件)。

编写测试激励(Testbench),运行功能仿真和时序仿真,观察输出波形是否符合设计预期-25。

核心价值:如果仿真结果正确但实际硬件输出错误,说明问题在硬件侧(供电、焊接、芯片损坏);如果仿真本身就出错,说明PLD文件或逻辑设计本身存在问题,需重新修改设计文件。

方法二:边界扫描(JTAG)板级测试

使用边界扫描控制器连接PCB上的JTAG接口。

运行边界扫描测试软件(如XJTAG、Corelis),自动生成测试向量,检测PLD与PCB上其他芯片之间的开路/短路-20。

优势:无需拆卸芯片即可完成板级互连测试,对多层板PCB尤其高效。

方法三:嵌入式逻辑分析仪在线捕获(针对FPGA类PLD)

在FPGA设计工程中插入SignalTapII嵌入式逻辑分析仪IP核(以Intel/Altera平台为例)。

配置采样时钟(通常用系统时钟)、触发条件和待观测信号节点,重新综合并烧录到FPGA中-39。

运行后,当触发条件满足时,SignalTap自动采集内部信号波形并上传到Quartus界面进行可视化分析。

工业场景应用:这种方式特别适合工业设备中偶发性故障的定位——如电机控制信号在特定转速下出现毛刺,传统外接示波器无法捕获芯片内部深层次信号,而嵌入式逻辑分析仪可以“内窥”芯片内部状态,极大提升调试效率-39。

方法四:内建自测试(BIST)执行

若PLD设计中已预先植入BIST逻辑,可通过外部触发信号启动自测试流程。

BIST电路自动生成测试向量并分析响应,输出测试结果(PASS/FAIL)-20。

核心价值:测试速度快、无需昂贵外部设备,适合工厂批量出货前的快速筛查。

三、补充模块(行业场景化参考)

1. 工业嵌入式不同类型PLD检测重点

CPLD检测重点:CPLD配置数据存储在非易失性Flash单元中,掉电不丢失。检测时应重点关注配置数据的完整性和内部宏单元的逻辑正确性。常见检测方法包括边界扫描配置验证和功能仿真。CPLD的故障模式中,“配置不生效”往往提示编程器与芯片之间的JTAG通信异常或芯片配置寄存器损坏-25。

FPGA检测重点:FPGA为RAM型配置方式,每次上电需从外部配置存储器(如SPI Flash)加载数据。检测时应重点验证配置加载过程是否成功——可以用示波器观察配置引脚(如nCONFIG、CONF_DONE)的上电时序波形。FPGA的逻辑错误可能来自配置数据损坏,也可能是内部查找表(LUT)或Block RAM的物理缺陷。

混合信号PLD检测重点:同时包含数字逻辑和模拟功能的PLD(如TI的TPLD系列),检测时需要兼顾数字部分的逻辑验证和模拟部分的参数测量(如比较器阈值、振荡器频率等),通常需要借助厂商提供的配套工具(如TI InterConnect Studio)进行全功能验证-。

2. 工业嵌入式PLD检测常见误区(避坑指南)

| 误区 | 行业危害 | 正确做法 |

|---|---|---|

| 只测供电不测信号质量 | 供电纹波过大可能导致PLD逻辑误翻转,尤其在高频工业控制场景中危害极大 | 用示波器测量电源纹波,峰峰值应小于VCC×5% |

| 误将配置失败当成芯片损坏 | 浪费维修时间和备件成本,配置失败多为配置文件错误或下载线接触不良 | 先用“空白检查”确认芯片可识别,再用不同配置文件尝试编程 |

| 忽略环境温度对检测结果的影响 | 工业设备在高温车间(>60℃)或低温冷库(<0℃)运行时,PLD参数可能漂移 | 在设备实际工作环境温度下进行检测,或使用高低温试验箱模拟-25 |

| 用万用表直接测量I/O引脚输出电流 | 可能拉低引脚电平导致误判,甚至损坏PLD输出驱动电路 | 测量输出电流需在引脚与负载之间串入电流表,而非直接短路 |

| 忘记清除PLD内部旧配置 | 新旧配置冲突导致逻辑行为混乱,且很难从外部观测到异常 | 编程新配置前先执行“擦除”操作,清空芯片原有数据 |

3. 工业嵌入式PLD失效典型案例(实操参考)

案例一:工厂流水线电机控制板PLD时序违例

故障现象:某自动化生产线电机控制板在运行2-3小时后偶尔出现控制信号滞后,导致产品定位偏差。

检测过程:维修人员先用万用表测量PLD供电——3.3V稳定。再用示波器观察时钟输入,发现晶振输出波形正常。接入JTAG读取PLD配置校验通过。进一步用逻辑分析仪同时抓取控制信号输出与系统时钟,发现输出信号的建立时间在某些温度上升后低于规格要求。

原因分析:PLD设计中的时序约束设置不够严格,在正常工作温度下勉强,但产线环境温度升高(约45℃)后,逻辑路径延迟增加导致建立时间违例。这是典型的“隐性故障”,容易被误判为芯片老化或电源问题。

解决方案:重新在EDA软件中进行静态时序分析,收紧关键路径的时序约束,生成新的配置文件烧录后故障彻底排除。

案例二:汽车ECU中PLD因静电放电损坏

故障现象:某汽车电子控制单元在生产线上测试时,约3%的ECU出现CAN通信中断故障,但同一批次器件单独测试完好。

检测过程:用万用表测量故障ECU上PLD的I/O引脚,发现多个CAN收发器接口引脚对地短路(电阻<10Ω)。将故障PLD拆下后,用X射线检测确认芯片内部引线断裂,封装完好无外部损伤-25。

原因分析:生产线装配过程中防静电措施不到位,操作人员在干燥环境中未佩戴静电手环,累积静电通过CAN接口端子放电进入PLD,造成内部ESD防护单元击穿并引发引线断裂。

解决方案:排查生产线静电防护设施,要求所有接触ECU的操作人员必须佩戴静电手环;在ECU输入端增加TVS管加强ESD防护;对故障批次进行全检,更换损坏PLD-44。

四、结尾

1. PLD检测核心(工业嵌入式高效排查策略)

面对工业嵌入式系统中的PLD故障,推荐采用分级排查策略:

第一级:基础初筛(5分钟内完成)

目视检查 → 供电电压测量 → 对地导通测试 → 时钟/复位信号波形观察。这一级排查可解决约60%的现场故障,主要是物理损坏和供电异常问题。

第二级:仪器验证(15分钟内完成)

JTAG连接检测 → 配置完整性校验 → I/O引脚电平验证。这一级可定位约30%的故障,包括配置数据损坏和I/O驱动能力不足。

第三级:专业精测(30分钟以上)

EDA仿真验证 → 边界扫描测试 → 嵌入式逻辑分析仪捕获 → BIST自测试。这一级用于排除逻辑设计错误和深层时序问题。

工业场景下的排查逻辑:先硬后软、先外后内。先排查供电、焊接、连接等硬件层面的问题,再深入PLD配置和逻辑设计层面。

2. PLD检测价值延伸(工业维护与采购建议)

日常维护建议:建议每季度对工业设备中的PLD进行一次基础检测(供电电压测量、JTAG通信确认),并定期备份PLD的配置文件(JEDEC/POF/SOF文件)。配置文件丢失或损坏后无法恢复,将导致设备彻底瘫痪,而工厂中这一问题屡见不鲜-44。

采购建议:采购PLD时务必确认供货渠道的正规性,非原装或翻新片可能存在配置存储器寿命不足或ESD损伤隐患。选择知名原厂品牌(如Intel/Altera、AMD/Xilinx、Microchip、TI),并关注器件的工业温度等级(-40℃~85℃或-40℃~105℃),确保适配工厂实际工作环境。对于产线批量应用,建议预留5%~10%的备用芯片以备紧急更换。

校准建议:若使用编程器进行批量烧录,建议每3个月对编程器的输出电平进行校准,确保烧录电压符合芯片规格要求,避免因编程器老化导致批量性配置错误。

3. 互动交流(分享工业嵌入式PLD检测难题)

你在工厂产线或维修现场检测PLD时,遇到过哪些难以定位的“疑难杂症”?是供电正常却无法识别的JTAG通信故障,还是配置校验通过但功能异常的诡异现象?欢迎在评论区分享你的工业PLD检测难题和解决经验,一起交流提升。

如果本文对你有帮助,欢迎收藏转发,后续将继续分享工业电子元器件检测系列干货。如有具体PLD型号的检测疑问,也可在评论区留言,我会尽力解答。